Physical Unclonable Functions (PUFs)

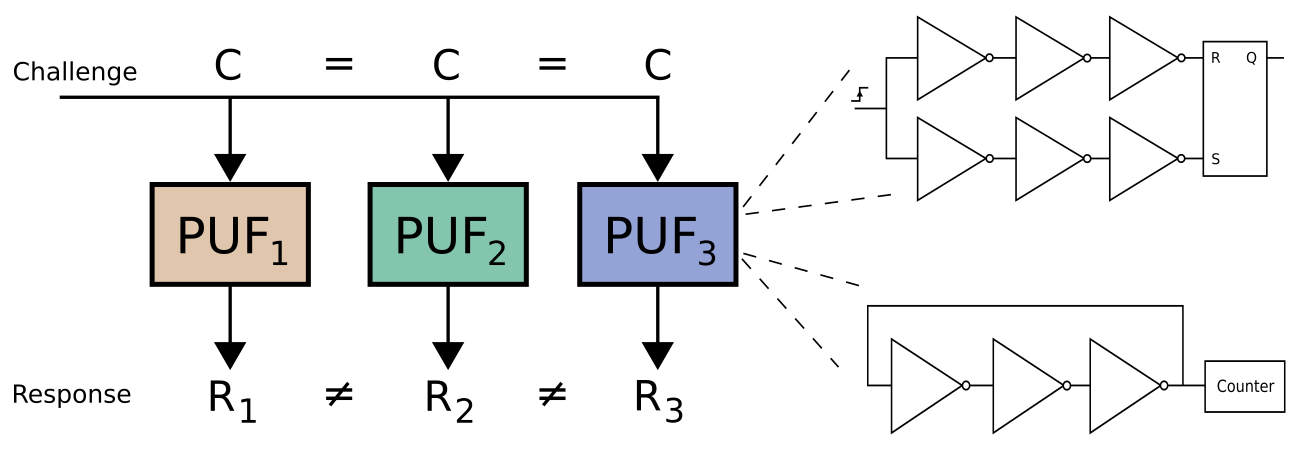

Over the last decade, Physical Unclonable Functions (PUF) became a topic of increasing interest in cryptographic and authentication applications. Utilizing physical variations in the silicon resulting from limited fabrication accuracy, PUFs offer great characteristics for this field namely uniqueness, unpredictability and unclonability. When stimulated with a digital input, they generate an individual digital response based on their unique mismatches.

Apart from a few novel PUF architectures and varying sources of mismatches, most recent publications mainly focus on improvements of existing PUF architectures by enhanced system level designs and improved coding/error correction techniques. Furthermore, the vast majority of new and/or improved designs are either simulated or implemented on FPGAs.

The focus of this project is to improve mixed-signal PUF architectures even further by mainly focusing on analog design technqiues to enhance existing PUF primitives and circuits on the transistor level. The goal is to achieve an advance in stability and quality of PUF responses, including immunity against environmental and noisy influences, higly unique behavior and stable readouts. Other side-topics emerging from this main research goal are improved methods of simulating enhanced PUF circuits and investigations on inventing new PUF architectures.

The second main topic of this project is investigating intrinsic PUFs, which can exist in consumer and industrial electronics or any other mixed-signal IC. Exploiting already existing circuits with inherent unique mismatches accessible and measurable from within the hosting system itself is a promising approach for rapid and chep implementable PUF architectures. This approach has been already investigated excessively on various types of memory and should be extended to other types of electronics.

Publications

The framework and measurement data of the publication "In-depth Analysis and Enhancements of RO-PUFs with a Partial Reconfiguration Framework on Xilinx Zynq-7000 SoC FPGAs" are provided under the following links: