XR-2211A FSK Demodulator/ Tone Decoder

September 1996-4

**EXAR** ... the analog plus company<sup>TM</sup>

# FEATURES

- Wide Frequency Range

0.01Hz to 300kHz

- Wide Supply Voltage Range 4.5V to 20V

- HCMOS/TTL/Logic Compatibility

- FSK Demodulation, with Carrier Detection

- Wide Dynamic Range 10mV to 3V rms

- Adjustable Tracking Range (<u>+</u>1% to 80%)

- Excellent Temp. Stability 100 ppm/°C, typ.

# APPLICATIONS

- Caller Identification Delivery

- FSK Demodulation

- Data Synchronization

- Tone Decoding

- FM Detection

- Carrier Detection

# **GENERAL DESCRIPTION**

The XR-2211A is a monolithic phase-locked loop (PLL) system especially designed for data communications applications. It is particularly suited for FSK modem applications. It operates over a wide supply voltage range of 4.5 to 20V and a wide frequency range of 0.01Hz to 300kHz. It can accommodate analog signals between 10mV and 3V, and can interface with conventional DTL, TTL, and ECL logic families. The circuit consists of a basic PLL for tracking an input signal within the pass band, a quadrature phase detector which provides carrier

detection, and an FSK voltage comparator which provides FSK demodulation. External components are used to independently set center frequency, bandwidth, and output delay. An internal voltage reference proportional to the power supply is provided at an output pin.

The XR-2211A is available in 14 pin packages specified for commercial temperature ranges.

# **ORDERING INFORMATION**

Rev. 1.01 ©1995

| Part No.   | Package                      | Operating<br>Temperature Range |

|------------|------------------------------|--------------------------------|

| XR-2211ACP | 14 Lead PDIP (0.300")        | 0°C to +70°C                   |

| XR-2211ACD | 14 Lead SOIC (Jedec, 0.150") | 0°C to +70°C                   |

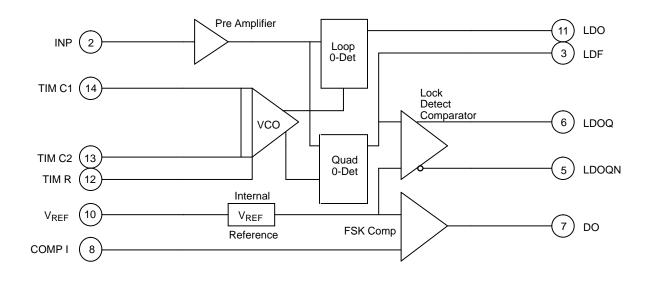

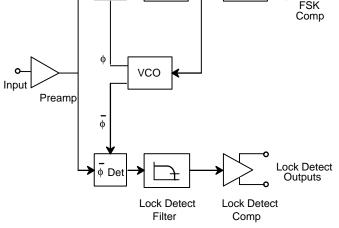

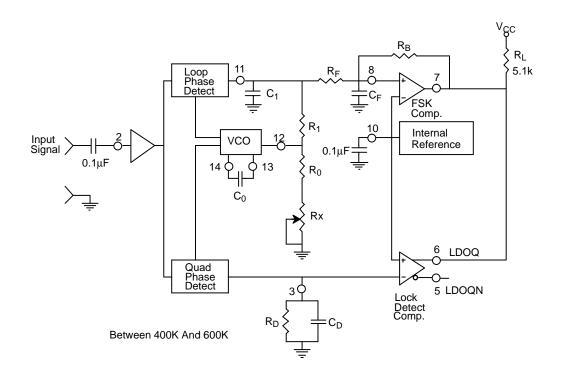

**BLOCK DIAGRAM**

Figure 1. XR-2211A Block Diagram

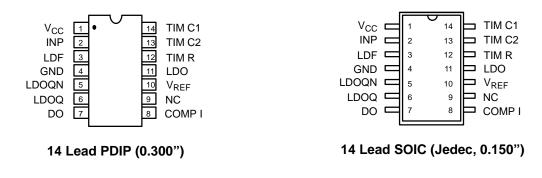

## **PIN CONFIGURATION**

#### **PIN DESCRIPTION**

| Pin # | Symbol           | Туре | Description                                                                            |  |  |  |

|-------|------------------|------|----------------------------------------------------------------------------------------|--|--|--|

| 1     | V <sub>CC</sub>  | -    | Positive power supply.                                                                 |  |  |  |

| 2     | INP              | I    | Receive Analog Input.                                                                  |  |  |  |

| 3     | LDF              | 0    | Lock detect filter.                                                                    |  |  |  |

| 4     | GND              | -    | Ground pin.                                                                            |  |  |  |

| 5     | LDOQN            | 0    | Lock detect output not. This output will be low if the VCO is in the capture range.    |  |  |  |

| 6     | LDOQ             | 0    | Lock detect output. This output will be high if the VCO is in the capture range.       |  |  |  |

| 7     | DO               | 0    | Data output. Decoded FSK output.                                                       |  |  |  |

| 8     | COMP I           | I    | FSK Comparator Input.                                                                  |  |  |  |

| 9     | NC               | -    | Not connected.                                                                         |  |  |  |

| 10    | V <sub>REF</sub> | 0    | Internal voltage reference. The value of $V_{REF}$ is $V_{CC}/2$ - 650mV.              |  |  |  |

| 11    | LDO              | 0    | Loop detect output. This output provides the result of the quadrature phase detection. |  |  |  |

| 12    | TIM R            | I    | Timing resistor input. This pin connects to the timing resistor of the VCO.            |  |  |  |

| 13    | TIM C2           | I    | Timing capacitor input. The timing capacitor connects between this pin and pin 14.     |  |  |  |

| 14    | TIM C1           | Ι    | Timing capacitor input. The timing capacitor connects between this pin and pin 13.     |  |  |  |

# **DC ELECTRICAL CHARACTERISTICS**

Test Conditions:  $V_{CC} = 12V$ ,  $T_A = +25^{\circ}C$ ,  $R_O = 30K\Omega$ ,  $C_O = 0.033\mu$ F, unless otherwise specified.

| Parameter                                              | Min.         | Тур.         | Max.         | Unit            | Conditions                                             |

|--------------------------------------------------------|--------------|--------------|--------------|-----------------|--------------------------------------------------------|

| GENERAL                                                |              |              |              |                 |                                                        |

| Supply Voltage                                         | 4.5          |              | 20           | V               |                                                        |

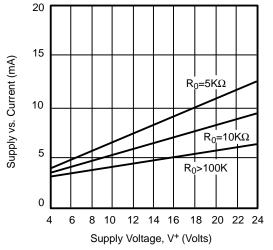

| Supply Current                                         |              | 5            | 9            | mA              | $R_0 \ge 10 k\Omega$ . See Figure 4.                   |

| Oscillator Section                                     | •            |              | •            | •               | -                                                      |

| Frequency Accuracy                                     |              | <u>+</u> 3   |              | %               | Deviation from $f_0 = 1/R_0 C_0$                       |

| Frequency Stability                                    |              |              |              |                 |                                                        |

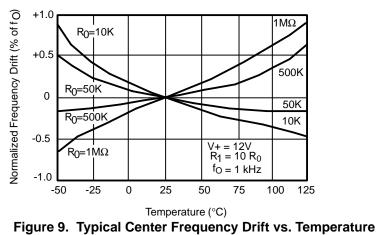

| Temperature                                            |              | <u>+</u> 100 |              | ppm/°C          | * See Figure 8.                                        |

| Power Supply                                           |              | 0.25         |              | %/V             | V <sub>CC</sub> = 12 <u>+</u> 1V. See <i>Figure 7.</i> |

|                                                        |              | 0.2          |              | %/V             | $V_{CC} = \pm 5.0V.$ See Figure 7.                     |

| Upper Frequency Limit                                  |              | 300          |              | kHz             | $R_0 = 8.2 k\Omega$ , $C_0 = 400 pF$                   |

| Lowest Practical                                       |              |              |              |                 |                                                        |

| Operating Frequency                                    |              | 0.01         |              | Hz              | $R_0 = 2M\Omega$ , $C_0 = 50\Omega F$                  |

| Timing Resistor, R <sub>0</sub> - See <i>Figure 5.</i> |              |              |              |                 |                                                        |

| Operating Range                                        | 5            |              | 2000         | KΩ              |                                                        |

| Recommended Range                                      | 5            |              | 100          | KΩ              | See Figure 7. and Figure 8.                            |

| Loop Phase Dectector Section                           | •            |              |              |                 |                                                        |

| Peak Output Current                                    | <u>+</u> 100 | <u>+</u> 200 | <u>+</u> 300 | μΑ              | Measured at Pin 11                                     |

| Output Offset Current                                  |              | <u>+</u> 2   |              | μΑ              |                                                        |

| Output Impedance                                       |              | 1            |              | MΩ              |                                                        |

| Maximum Swing                                          | <u>+</u> 4   | <u>+</u> 5   |              | V               | Referenced to Pin 10                                   |

| Quadrature Phase Detector                              |              |              |              |                 | Measured at Pin 3                                      |

| Peak Output Current                                    |              | 300          |              | μΑ              |                                                        |

| Output Impedance                                       |              | 1            |              | MΩ              |                                                        |

| Maximum Swing                                          |              | 11           |              | V <sub>PP</sub> |                                                        |

| Input Preampt Section                                  | -            |              | •            | •               | Measured at pin 2                                      |

| Input Impedance                                        |              | 20           |              | KΩ              |                                                        |

| Input Signal                                           |              |              |              |                 |                                                        |

| Voltage Required to<br>Cause Limiting                  |              | 2            |              | mVrms           |                                                        |

#### Note:

- These parameters, although guaranteed over the recommended operating conditions, are not 100% tested in production.

- Bold face parameters are covered by production test.

# DC ELECTRICAL CHARACTERISTICS (Cont.)

Test Conditions:  $V_{CC} = 12V$ ,  $T_A = +25^{\circ}C$ ,  $R_O = 30K\Omega$ ,  $C_O = 0.033\mu$ F, unless otherwise specified.

| Parameter                  | Min. | Тур. | Max. | Unit | Conditions               |  |

|----------------------------|------|------|------|------|--------------------------|--|

| Voltage Comparator Section |      |      |      |      |                          |  |

| Input Impedance            |      | 2    |      | MΩ   | Measured at pins 3 and 8 |  |

| Input Bias Current         |      | 100  |      | nA   |                          |  |

| Voltage Gain               | 55   | 70   |      | dB   | $R_L = 5.1 K\Omega$      |  |

| Output Voltage Low         |      | 300  | 500  | mV   | I <sub>C</sub> = 3mA     |  |

| Output Leakage Current     |      | 0.01 | 10   | μA   | $V_0 = 20V$              |  |

| Internal Reference         |      |      | •    | •    | -                        |  |

| Voltage Level              | 4.75 | 5.3  | 5.85 | V    | Measured at pin 10       |  |

| Output Impedance           |      | 100  |      | Ω    | AC Small Signal          |  |

| Maximum Source Current     |      | 80   |      | μA   |                          |  |

Note:

- These parameters, although guaranteed over the recommended operating conditions, are not 100% tested in production.

- Bold face parameters are covered by production test.

#### Specifications are subject to change without notice

#### **ABSOLUTE MAXIMUM RATINGS**

| Power Supply             | V |

|--------------------------|---|

| Input Signal Level 3V rm | s |

| Power Dissipation 900mV  | V |

| Plastic Package                   | 800mW  |

|-----------------------------------|--------|

| Derate Above $T_A = +25^{\circ}C$ | 6mW/°C |

| JEDEC SOIC                        | 390mW  |

| Derate Above $T_A = +25^{\circ}C$ | 5mW/°C |

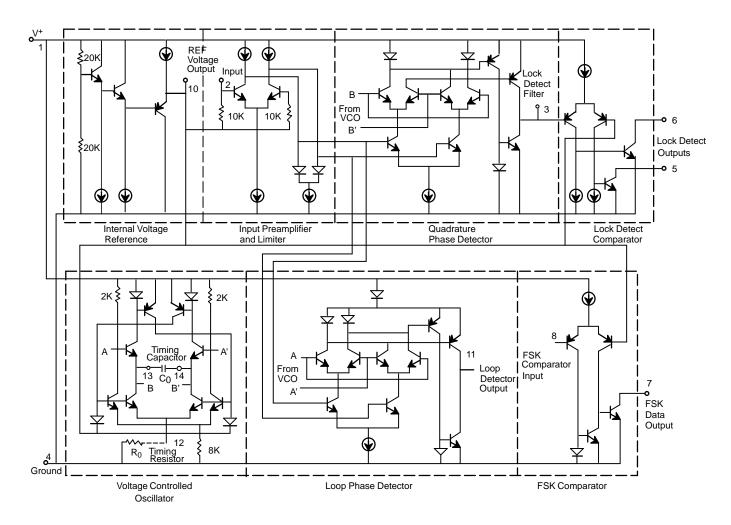

#### SYSTEM DESCRIPTION

The main PLL within the XR-2211A is constructed from an input preamplifier, analog multiplier used as a phase detector and a precision voltage controlled oscillator (VCO). The preamplifier is used as a limiter such that input signals above typically 10mV RMS are amplified to a constant high level signal. The multiplying-type phase detector acts as a digital exclusive or gate. Its output (unfiltered) produces sum and difference frequencies of the input and the VCO output. The VCO is actually a current controlled oscillator with its normal input current ( $f_O$ ) set by a resistor ( $R_0$ ) to ground and its driving current with a resistor ( $R_1$ ) from the phase detector.

The output of the phase detector produces sum and difference of the input and the VCO frequencies

(internally connected). When in lock, these frequencies are  $f_{IN}$ +  $f_{VCO}$  (2 times  $f_{IN}$  when in lock) and  $f_{IN}$  -  $f_{VCO}$  (0Hz when lock). By adding a capacitor to the phase detector output, the 2 times  $f_{IN}$  component is reduced, leaving a DC voltage that represents the phase difference between the two frequencies. This closes the loop and allows the VCO to track the input frequency.

The FSK comparator is used to determine if the VCO is driven above or below the center frequency (FSK comparator). This will produce both active high and active low outputs to indicate when the main PLL is in lock (quadrature phase detector and lock detector comparator).

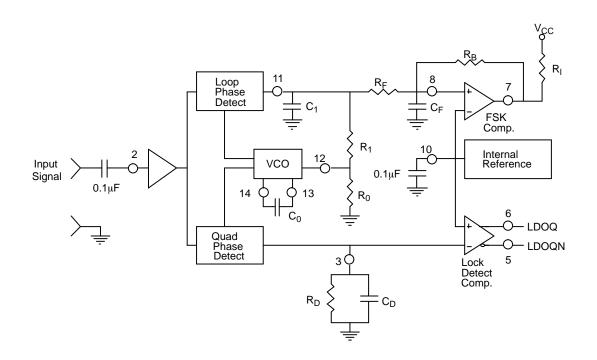

**Signal Input (pin 2):** Signal is AC coupled to this terminal. The internal impedance at pin 2 is  $20K\Omega$ . Recommended input signal level is in the range of 10mV rms to 3V rms.

**Quadrature Phase Detector Output (pin 3):** This is the high impedance output of quadrature phase detector and is internally connected to the input of lock detect voltage comparator. In tone detection applications, pin 3 is connected to ground through a parallel combination of  $R_D$  and  $C_D$  (see *Figure 3*.) to eliminate the chatter at lock detect outputs. If the tone detect section is not used, pin 3 can be left open.

**Lock Detect Output, Q (pin 6):** The output at pin 6 is at "low" state when the PLL is out of lock and goes to "high" state when the PLL is locked. It is an open collector type output and requires a pull-up resistor,  $R_L$ , to  $V_{CC}$  for proper operation. At "low" state, it can sink up to 5mA of load current.

**Lock Detect Complement, (pin 5):** The output at pin 5 is the logic complement of the lock detect output at pin 6. This output is also an open collector type stage which can sink 5mA of load current at low or "on" state.

**FSK Data Output (pin 7):** This output is an open collector logic stage which requires a pull-up resistor,  $R_L$ , to  $V_{CC}$  for proper operation. It can sink 5mA of load current. When decoding FSK signals, FSK data output is at "high" or "off" state for low input frequency, and at "low" or "on" state for high input frequency. If no input signal is present, the logic state at pin 7 is indeterminate.

**FSK Comparator Input (pin 8):** This is the high impedance input to the FSK voltage comparator. Normally, an FSK post-detection or data filter is connected between this terminal and the PLL phase detector output (pin 11). This data filter is formed by  $R_F$  and  $C_F$  (see *Figure 3.*). The threshold voltage of the comparator is set by the internal reference voltage,  $V_{REF}$ , available at pin 10.

**Reference Voltage, V<sub>REF</sub> (pin 10):** This pin is internally biased at the reference voltage level,  $V_{REF}$ :  $V_{REF} = V_{CC}/2$  - 650mV. The DC voltage level at this pin forms an internal reference for the voltage levels at pins 5, 8, 11 and 12. Pin 10 must be bypassed to ground with a 0.1µF capacitor for proper operation of the circuit.

**Loop Phase Detector Output (pin 11):** This terminal provides a high impedance output for the loop phase detector. The PLL loop filter is formed by  $R_1$  and  $C_1$  connected to pin 11 (see *Figure 3.*). With no input signal, or with no phase error within the PLL, the DC level at pin 11 is very nearly equal to  $V_{REF}$ . The peak to peak voltage swing available at the phase detector output is equal to 2 x  $V_{REF}$ .

**VCO Control Input (pin 12):** VCO free-running frequency is determined by external timing resistor,  $R_0$ , connected from this terminal to ground. The VCO free-running frequency,  $f_0$ , is:

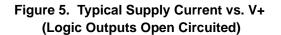

$$f_O = \frac{1}{R_0 \cdot C_0} Hz$$

where  $C_0$  is the timing capacitor across pins 13 and 14. For optimum temperature stability,  $R_0$  must be in the range of  $10K\Omega$  to  $100K\Omega$  (see *Figure 9.*).

This terminal is a low impedance point, and is internally biased at a DC level equal to  $V_{REF}$ . The maximum timing current drawn from pin 12 must be limited to  $\leq$  3mA for proper operation of the circuit.

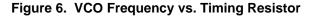

**VCO Timing Capacitor (pins 13 and 14):** VCO frequency is inversely proportional to the external timing capacitor,  $C_0$ , connected across these terminals (see *Figure 6.*).  $C_0$  must be non-polar, and in the range of 200pF to 10 $\mu$ F.

**VCO Frequency Adjustment:** VCO can be fine-tuned by connecting a potentiometer,  $R_X$ , in series with  $R_0$  at pin 12 (see *Figure 10.*).

**VCO Free-Running Frequency,**  $f_0$ : XR-2211A does not have a separate VCO output terminal. Instead, the VCO outputs are internally connected to the phase detector sections of the circuit. For set-up or adjustment purposes, the VCO free-running frequency can be tuned by using the generalized circuit in *Figure 3.*, and applying an alternating bit pattern of O's and 1's at the known mark and space frequencies. By adjusting R<sub>0</sub>, the VCO can then be tuned to obtain a 50% duty cycle on the FSK output (pin 7). This will ensure that the VCO f<sub>0</sub> value is accurately referenced to the mark and space frequencies.

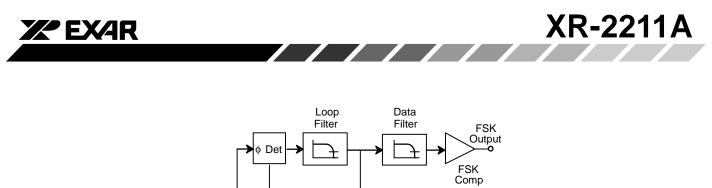

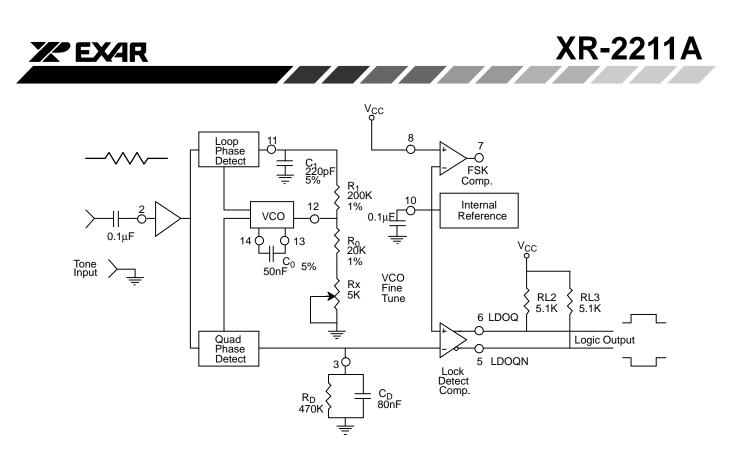

Figure 2. Functional Block Diagram of a Tone and FSK Decoding System Using XR-2211A

Figure 3. Generalized Circuit Connection for FSK and Tone Detection

## **DESIGN EQUATIONS**

(All resistance in Ω, all frequency in Hz and all capacitance in farads, unless otherwise specified)

(See Figure 3. for definition of components)

1. VCO Center Frequency, fo:

$$f_O = \frac{1}{R_0 \cdot C_0}$$

2. Internal Reference Voltage, V<sub>REF</sub> (measured at pin 10):

$$V_{REF} = \left(\frac{V_{CC}}{2}\right) - 650 mV$$

in volts

3. Loop Low-Pass Filter Time Constant, τ:

$$\tau = C_1 \cdot R_{PP}$$

(seconds)

where:

$$R_{PP} = \left(\frac{R_1 \cdot R_F}{R_1 + R_F}\right)$$

if  $R_F$  is  $\infty$  or  $C_F$  reactance is  $\infty$ , then  $R_{PP}$  = R1

4. Loop Damping, ς:

$$\zeta = \sqrt{\left(\frac{1250 \cdot C_0}{R_1 \cdot C_1}\right)}$$

Note: For derivation/explanation of this equation, please see TAN-011.

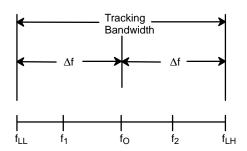

5. Loop-tracking

bandwidth,  $\pm = \frac{\Delta f}{f_0}$  $\frac{\Delta f}{f_0} = \frac{R_0}{R_1}$

6. FSK Data filter time constant, tF:

$$\tau_F = \frac{R_B \cdot R_F}{(R_B + R_F)} \cdot C_F \text{ (seconds)}$$

7. Loop phase detector conversion gain, Kd: (Kd is the differential DC voltage across pin 10 and pin11, per unit of phase error at phase detector input):

$$K_{d} = \frac{V_{REF} \cdot R_{1}}{10,000 \cdot \pi} \left[ \frac{volt}{radian} \right]$$

Note: For derivation/explanation of this equation, please see TAN-011.

8. VCO conversion gain, Ko: (Ko is the amount of change in VCO frequency, per unit of DC voltage change at pin 11):

$$K_0 = \frac{-2\pi}{V_{REF} \cdot C_0 \cdot R_1} = \left(\frac{radian/second}{volt}\right)$$

9. The filter transfer function:

$$F(s) = \frac{1}{1 + SR_1 \cdot C_1} \text{ at } 0 \text{ Hz.} \qquad S = J\omega \text{ and } \omega = 0$$

10. Total loop gain. K<sub>T</sub>:

$$K_{T} = K_{O} \cdot K_{o'} F(s) = \left(\frac{R_{F}}{5,000 \cdot C_{0} \cdot (R_{1} + R_{F})}\right) \left[\frac{1}{seconds}\right]$$

11. Peak detector current I<sub>A</sub>:

$$I_A = \frac{V_{REF}}{20,000}$$

( $V_{REF}$  in volts and  $I_A$  in amps)

Note: For derivation/explanation of this equation, please see TAN-011.

#### **APPLICATIONS INFORMATION**

#### **FSK Decoding**

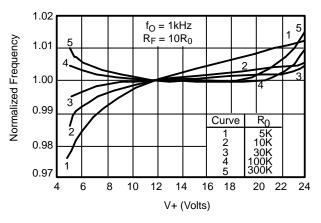

*Figure 10.* shows the basic circuit connection for FSK decoding. With reference to *Figure 3.* and *Figure 10.*, the functions of external components are defined as follows:  $R_0$  and  $C_0$  set the PLL center frequency,  $R_1$  sets the system bandwidth, and  $C_1$  sets the loop filter time constant and the loop damping factor.  $C_F$  and  $R_F$  form a one-pole post-detection filter for the FSK data output. The resistor  $R_B$  from pin 7 to pin 8 introduces positive feedback across the FSK comparator to facilitate rapid transition between output logic states.

**XPEXAR**

#### **Design Instructions:**

The circuit of *Figure 10.* can be tailored for any FSK decoding application by the choice of five key circuit components:  $R_0$ ,  $R_1$ ,  $C_0$ ,  $C_1$  and  $C_F$ . For a given set of FSK mark and space frequencies,  $f_0$  and  $f_1$ , these parameters can be calculated as follows:

(All resistance in Ω's, all frequency in Hz and all capacitance in farads, unless otherwise specified)

a) Calculate PLL center frequency, f<sub>O</sub>:

$$f_O = \sqrt{F_1 \cdot F_2}$$

b) Choose value of timing resistor  $R_0$ , to be in the range of  $10K\Omega$  to  $100K\Omega$ . This choice is arbitrary. The recommended value is  $R_0 = 20K\Omega$ . The final value of  $R_0$  is normally fine-tuned with the series potentiometer,  $R_X$ .

$$R_o = R_o + \frac{R_X}{2}$$

c) Calculate value of C0 from design equation (1) or from Figure 7.:

$$C_{O} = \frac{1}{R_{0} \cdot f_{0}}$$

d) Calculate R1 to give the desired tracking bandwidth (See design equation 5).

$$R_{1} = \frac{R_{0} \cdot f_{0}}{(f_{1} - f_{2})} \cdot 2$$

e) Calculate C1 to set loop damping. (See design equation 4): Normally,  $\varsigma = 0.5$  is recommended.

$$C_1 = \frac{1250 \cdot C_0}{R_1 \cdot \varsigma^2}$$

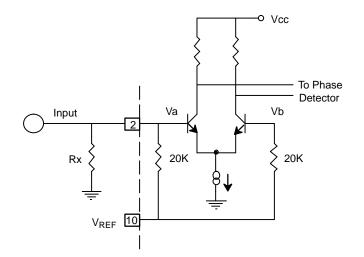

The input to the XR-2211A may sometimes be too sensitive to noise conditions on the input line. Figure 4. illustrates f) a method of de-sensitizing the XR-2211A from such noisy line conditions by the use of a resistor, Rx, connected from pin 2 to ground. The value of Rx is chosen by the equation and the desired minimum signal threshold level.

$V_{IN}$  minimum (peak) =  $V_a - V_b = \Delta V \pm 2.8 mV$  offset =  $V_{REF} \frac{20,000}{(20,000 + R_X)}$  or  $R_X = 20,000 \left(\frac{V_{REF}}{\Delta V} - 1\right)$

VIN minimum (peak) input voltage must exceed this value to be detected (equivalent to adjusting V threshold)

Figure 4. Desensitizing Input Stage

1

Calculate Data Filter Capacitance, C<sub>F</sub>: g)

$$R_{sum} = \frac{(R_F + R_1) \cdot R_B}{(R_1 + R_F + R_B)}$$

$$C_F = \frac{250}{R_{sum} \cdot (Baud \ Rate)}$$

Baud rate in  $\frac{1}{seconds}$

**Note:** All values except  $R_0$  can be rounded to nearest standard value.

1.0  $R_0=5K\Omega$ ┦  $R_0=10K\Omega$ C<sub>0</sub>( µF)  $R_0=20K\Omega$ 0.  $R_0=40K\Omega$  $R_0=80K\Omega$  $\mathbb{N}$  $R_0 = 160 \hat{K}\Omega$ 0.01 1000 100 10000 f<sub>O</sub>(HZ)

**XPEXAR**

Figure 8. Typical f<sub>O</sub> vs. Power Supply Characteristics

## Design Example:

### 1200 Baud FSK demodulator with mark and space frequencies of 1200/2200.

Step 1: Calculate f<sub>O</sub>: from design instructions

(a)

$$f_o = \sqrt{1200.2200} = 1624$$

Step 2: Calculate  $R_0$ :  $R_0 = 10K$  with a potentiometer of 10K. (See design instructions (b))

(b)

$$R_{\tau} = 10 + \left(\frac{10}{2}\right) = 15K$$

Step 3: Calculate C<sub>0</sub> from design instructions

(c)

$$C_o = \frac{1}{15000 \cdot 1624} = 39 nF$$

Step 4: Calculate R<sub>1</sub> : from design instructions

(d)

$$R_1 = \frac{20000 \cdot 1624 \cdot 2}{(2200 - 1200)} = 51,000$$

Step 5: Calculate C1 : from design instructions

(e)

$$C_1 = \frac{1250 \cdot 39nF}{51000 \cdot 0.5^2} = 3.9nF$$

Step 6: Calculate  $R_F$ :  $R_F$  should be at least five times  $R_1$ ,  $R_F = 51,000.5 = 255 \text{ K}\Omega$ Step 7: Calculate  $R_B$ :  $R_B$  should be at least five times  $R_F$ ,  $R_B = 255,000.5 = 1.2 \text{ M}\Omega$ Step 8: Calculate  $R_{SUM}$ :

$$R_{SUM} = \frac{(R_F + R_1) \cdot R_B}{(R_F + R_1 + R_B)} = 240 K\Omega$$

Step 9: Calculate CF:

$$C_F = \frac{250}{(R_{SUM} \cdot Baud Rate)} = 1nF$$

**Note:** All values except R<sub>0</sub> can be rounded to nearest standard value.

Figure 10. Circuit Connection for FSK Decoding of Caller Identification Signals (Bell 202 Format)

Figure 11. External Connectors for FSK Demodulation with Carrier **Detect Capability**

Figure 12. Circuit Connection for Tone Detection

#### **FSK Decoding with Carrier Detect**

The lock detect section of XR-2211A can be used as a carrier detect option for FSK decoding. The recommended circuit connection for this application is shown in *Figure 11*. The open collector lock detect output, pin 6, is shorted to data output (pin 7). Thus, data output will be disabled at "low" state, until there is a carrier within the detection band of the PLL and the pin 6 output goes "high" to enable the data output.

#### Note: Data Output is "Low" When No Carrier is Present.

The minimum value of the lock detect filter capacitance  $C_D$  is inversely proportional to the capture range,  $\pm\Delta fc$ . This is the range of incoming frequencies over which the loop can acquire lock and is always less than the tracking range. It is further limited by  $C_1$ . For most applications,  $\Delta fc > \Delta f/2$ . For  $R_D = 470 K\Omega$ , the approximate minimum value of  $C_D$  can be determined by:

$$C_D > \frac{16}{\Delta f}$$

C in  $\mu$ F and f in Hz.

#### C in $\mu$ F and f in Hz.

With values of  $C_D$  that are too small, chatter can be observed on the lock detect output as an incoming signal

frequency approaches the capture bandwidth. Excessively large values of  $C_D$  will slow the response time of the lock detect output. For Caller I.D. applications choose  $C_D = 0.1 \mu F$ .

#### **Tone Detection**

*Figure 12.* shows the generalized circuit connection for tone detection. The logic outputs, LDOQN and LDOQ at pins 5 and 6 are normally at "high" and "low" logic states, respectively. When a tone is present within the detection band of the PLL, the logic state at these outputs become reversed for the duration of the input tone. Each logic output can sink 5mA of load current.

Both outputs at pins 5 and 6 are open collector type stages, and require external pull-up resistors  $R_{L2}$  and  $R_{L3}$ , as shown in *Figure 12*.

With reference to *Figure 3.* and *Figure 12.*, the functions of the external circuit components can be explained as follows:  $R_0$  and  $C_0$  set VCO center frequency;  $R_1$  sets the detection bandwidth;  $C_1$  sets the low pass-loop filter time constant and the loop damping factor.

## **Design Instructions:**

The circuit of *Figure 12.* can be optimized for any tone detection application by the choice of the 5 key circuit components:  $R_0$ ,  $R_1$ ,  $C_0$ ,  $C_1$  and  $C_D$ . For a given input, the tone frequency,  $f_S$ , these parameters are calculated as follows:

(All resistance in Ω's, all frequency in Hz and all capacitance in farads, unless otherwise specified)

- a) Choose value of timing resistor R<sub>0</sub> to be in the range of 10K $\Omega$  to 50K $\Omega$ . This choice is dictated by the max./min. current that the internal voltage reference can deliver. The recommended value is R<sub>0</sub> = 20K $\Omega$ . The final value of R<sub>0</sub> is normally fine-tuned with the series potentiometer, R<sub>X</sub>.

- b) Calculate value of  $C_0$  from design equation (1) or from *Figure 7*.  $f_S = f_O$ :

$$C_{O} = \frac{1}{R_{0} \cdot fs}$$

c) Calculate  $R_1$  to set the bandwidth  $\pm \Delta f$  (See design equation 5):

$$R_1 = \frac{R_0 \cdot f_0 \cdot 2}{\varDelta f}$$

**Note:** The total detection bandwidth covers the frequency range of  $f_O \pm \Delta f$

d) Calculate value of C1 for a given loop damping factor:

Normally,  $\varsigma = 0.5$  is recommended.

$$C_1 = \frac{1250 \cdot C_0}{R_1 \cdot \varsigma^2}$$

Increasing C1 improves the out-of-band signal rejection, but increases the PLL capture time.

e) Calculate value of the filter capacitor  $C_D$ . To avoid chatter at the logic output, with  $R_D = 470 K\Omega$ ,  $C_D$  must be:

$$C_D > \frac{16}{\varDelta f}$$

C in  $\mu F$

Increasing C<sub>D</sub> slows down the logic output response time.

#### **Design Examples:**

Tone detector with a detection band of  $\pm$  100Hz:

- a) Choose value of timing resistor R<sub>0</sub> to be in the range of 10K $\Omega$  to 50K $\Omega$ . This choice is dictated by the max./min. current that the internal voltage reference can deliver. The recommended value is R<sub>0</sub> = 20 K $\Omega$ . The final value of R<sub>0</sub> is normally fine-tuned with the series potentiometer, R<sub>X</sub>.

- b) Calculate value of  $C_0$  from design equation (1) or from *Figure 6*.  $f_S = f_O$ :

$$C_0 = \frac{1}{R_0 \cdot f_s} = \frac{1}{20,000 \cdot 1,000} = 50 nF$$

c) Calculate  $R_1$  to set the bandwidth  $\pm \Delta f$  (See design equation 5):

$$R_1 = \frac{R_0 \cdot f_0 \cdot 2}{\Delta f} = \frac{20,000 \cdot 1,000 \cdot 2}{100} = 400K$$

**Note:** The total detection bandwidth covers the frequency range of  $f_O \pm \Delta f$

d) Calculate value of  $C_0$  for a given loop damping factor:

Normally,  $\varsigma = 0.5$  is recommended.

$$C_1 = \frac{1250 \cdot C_0}{R_1 \cdot S^2} = \frac{1250 \cdot 50 \cdot 10^{-9}}{400,000 \cdot 0.5^2} = 6.25 pF$$

Increasing C<sub>1</sub> improves the out-of-band signal rejection, but increases the PLL capture time.

e) Calculate value of the filter capacitor  $C_D$ . To avoid chatter at the logic output, with  $R_D = 470 K\Omega$ ,  $C_D$  must be:

$$C_D = \frac{16}{\varDelta f} \ge \frac{16}{200} \ge 80 nF$$

Increasing C<sub>D</sub> slows down the logic output response time.

f) Fine tune center frequency with 5K $\Omega$  potentiometer, R<sub>X</sub>.

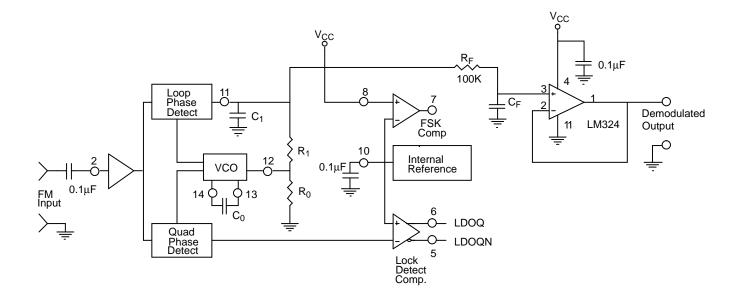

Figure 13. Linear FM Detector Using XR-2211A and an External Op Amp. (See Section on Design Equation for Component Values.)

#### Linear FM Detection

XR-2211A can be used as a linear FM detector for a wide range of analog communications and telemetry applications. The recommended circuit connection for this application is shown in Figure 13. The demodulated output is taken from the loop phase detector output (pin 11), through a post-detection filter made up of R<sub>F</sub> and C<sub>F</sub>, and an external buffer amplifier. This buffer amplifier is necessary because of the high impedance output at pin 11. Normally, a non-inverting unity gain op amp can be used as a buffer amplifier, as shown in Figure 13.

The FM detector gain, i.e., the output voltage change per unit of FM deviation can be given as:

$$V_{OUT} = \frac{R_1 \cdot V_{REF}}{100 \cdot R_0}$$

where VR is the internal reference voltage ( $V_{REF} = V_{CC}/2$ - 650mV). For the choice of external components R<sub>1</sub>, R<sub>0</sub>,  $C_D$ ,  $C_1$  and  $C_F$ , see the section on design equations.

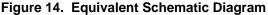

# 14 LEAD PLASTIC DUAL-IN-LINE (300 MIL PDIP)

Rev. 1.00

|                | INC   | HES    | MILLIN   | <b>METERS</b> |

|----------------|-------|--------|----------|---------------|

| SYMBOL         | MIN   | MAX    | MIN      | MAX           |

| А              | 0.145 | 0.210  | 3.68     | 5.33          |

| A <sub>1</sub> | 0.015 | 0.070  | 0.38     | 1.78          |

| A <sub>2</sub> | 0.115 | 0.195  | 2.92     | 4.95          |

| В              | 0.014 | 0.024  | 0.36     | 0.56          |

| B <sub>1</sub> | 0.030 | 0.070  | 0.76     | 1.78          |

| С              | 0.008 | 0.014  | 0.20     | 0.38          |

| D              | 0.725 | 0.795  | 18.42    | 20.19         |

| E              | 0.300 | 0.325  | 7.62     | 8.26          |

| E <sub>1</sub> | 0.240 | 0.280  | 6.10     | 7.11          |

| е              | 0.1   | 00 BSC | 2.5      | 4 BSC         |

| e <sub>A</sub> | 0.3   | 00 BSC | 7.62 BSC |               |

| e <sub>B</sub> | 0.310 | 0.430  | 7.87     | 10.92         |

| L              | 0.115 | 0.160  | 2.92     | 4.06          |

| α              | 0°    | 15°    | 0°       | 15°           |

Note: The control dimension is the inch column

T�M

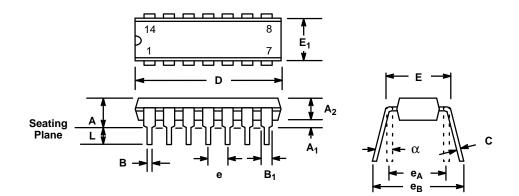

14 LEAD SMALL OUTLINE (150 MIL JEDEC SOIC)

Rev. 1.00

|                | INC   | HES    | MILLIMETERS |      |

|----------------|-------|--------|-------------|------|

| SYMBOL         | MIN   | МАХ    | MIN         | MAX  |

| А              | 0.053 | 0.069  | 1.35        | 1.75 |

| A <sub>1</sub> | 0.004 | 0.010  | 0.10        | 0.25 |

| В              | 0.013 | 0.020  | 0.33        | 0.51 |

| С              | 0.007 | 0.010  | 0.19        | 0.25 |

| D              | 0.337 | 0.344  | 8.55        | 8.75 |

| E              | 0.150 | 0.157  | 3.80        | 4.00 |

| е              | 0.0   | 50 BSC | 1.27 BSC    |      |

| Н              | 0.228 | 0.244  | 5.80        | 6.20 |

| L              | 0.016 | 0.050  | 0.40        | 1.27 |

| α              | 0°    | 8°     | 0°          | 8°   |

ζα

L

Note: The control dimension is the millimeter column

Notes

Notes

Notes

# NOTICE

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained here in are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Copyright 1995 EXAR Corporation Datasheet September 1996 Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.