High-Resolution Incremental Sigma Delta ADCs for Biomedical Signals

In the past few years, an increased interest in biomedical implants like neural recorders is noticeable as measured by the number of publications. These devices are integrated circuits (ICs) that comprise more and more functionality which increases their versatility and importance in medical research.

One field of application of these recorders is the investigation of nervous tissue, for example. Neural recorders make it possible to record the response of nervous tissue after current/voltage stimulation. This may make it possible in the future to provide precise diagnosis for patients or to adapt stimulation parameters precisely to every individual patient.

The recording action is performed by a dedicated ADC that is integrated within the neural recorder IC. As the voltage levels of neural signals are known to be very small in a noisy environment it is of prime importance to use an ADC that features a large dynamic range to be able to resolve these signals down to the noise floor for further digital processing. As the implant is used in a critical environment, i.e. the brain, that must not be heated up, these ADCs are very limited in terms of area and power consumption, respectively.

To fulfill these requirements, ΣΔ ADCs seem to be an appropriate choice due to their properties like oversampling and noise shaping which trade speed for accuracy. This makes it possible to realize ADCs with an extremely high resolution. Unfortunately, these ADCs have memory, which makes them less attractive as Neural recorders usually feature large electrode arrays with up to 1000 elements. Thus, it would be necessary to use one ADC per electrode which results in a system that could never fulfil the area and power constraints.

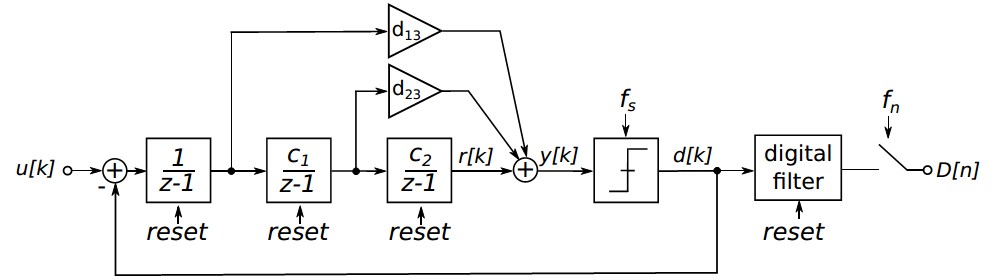

Therefore, incremental ΣΔ (I-ΣΔ) ADCs have been researched that feature “memoryless” operation which makes it possible to convert multiple electrodes by one dedicated ADC through multiplexing between different electrodes. This can be achieved by periodically resetting the modulator after OSR cycles as displayed in Figure 1 at hands of an exemplary third order CIFF I-ΣΔ modulator.

Even though high-resolution I-ΣΔ have been researched in the past, much less attention was paid to their different behavior compared with free running ΣΔ ADCs. Therefore, the functionality of these modulators is not entirely understood, which leaves room for improvement of the effectiveness of these modulators on architectural and circuit level.

Dr.-Ing. Patrick Vogelmann