Background Correction in Sigma Delta A/D Converters

There exist plenty of possibilities for the correction of non-idealities in CT SD Modulators, e.g. for coefficient mismatch, excess loop delay, D/A error correction and others. Nonetheless, most of the existing approaches rely on offline correction or even a priori known behaviour of the circuit.

One example for offline calibration has been published in 2005 (IEEE Trans. on Circuits and Systems I, Vol.52), where the gain error in cascaded continuous-time SD modulators has been corrected by digital filter adaption. Therefore, the output bit activity (number of transitions of output bits due to noise) of the decimation filter has been minimized iteratively without modulator input signal. Therewith, optimal performance can be achieved.

On the other hand, on-line correction during the normal operation of the circuit is more favourable since the user or application is not aware of the calibration, which is therefore called background. Often, background calibration either needs a significantly increased hardware effort, since background calibration is done using redundant circuitry, is done in time instants, where the hardware is not needed, or significantly reduces the performance of the system while the calibration is running.

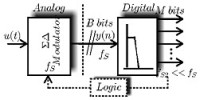

Our research focuses on background calibration and correction of SD A/D converters, which track the system into its optimal operating point in a closed loop procedure. The investigated techniques use either test signal injection or work completely blind on the circuits output signal.