Leistungseffiziente Deep Neural Networks basierend auf der Co-Optimierung mit Mixed-Signal Integrierten Schaltungen

EdgeAI ist das verteilte Computing-Paradigma für die Ausführung von Machine-Learning-Algorithmen in der Nähe des Sensors. Im Vergleich zu zentralisierten, z. B. Cloud-basierten Lösungen werden Datensicherheit, niedrige Latenzzeiten und geringere Bandbreiten erreicht. Gleichzeitig besteht das große Problem, dass der Stromverbrauch der heutigen tiefen neuronalen Netze (die häufigste Art von Machine-Learning-Algorithmen) für solche Anwendungen viel zu hoch ist. Moderne Netzwerkarchitekturen sind komplex und stellen hohe Anforderungen an die Rechenressourcen. Dieses Problem wird auf zwei Arten angegangen.

Erstens kann der Rechenaufwand des neuronalen Netzes durch Beschneidung oder Quantisierung von Operanden reduziert werden. Dies wird gemeinhin als Netzkompression bezeichnet.

Eine zweite Möglichkeit, den Einsatz von KI-Algorithmen am Edge zu ermöglichen, ist der Einsatz spezialisierter Beschleuniger (Prozessoren), um ein häufiges Problem zu lösen: KI-Algorithmen erfordern in der Regel die Übertragung großer Datenmengen zwischen Speicher und Berechnung. Dieses Problem wird als von-Neumann-Engpass bezeichnet. Die Lösung besteht darin, die Rechen- und Speicherelemente innerhalb der Architektur des Beschleunigers zu verteilen und zu mischen.

In diesem Projekt werden verschiedene Aspekte untersucht, bei denen die Optimierung von Hardware und Algorithmus als gemeinsames Problem behandelt werden muss. Die betrachteten Hardware-Plattformen sind Mixed-Signal-Beschleuniger, die analoge Größen (Ladung, Spannung, Strom) zur Darstellung von Operanden innerhalb einer AI-Berechnung verwenden.

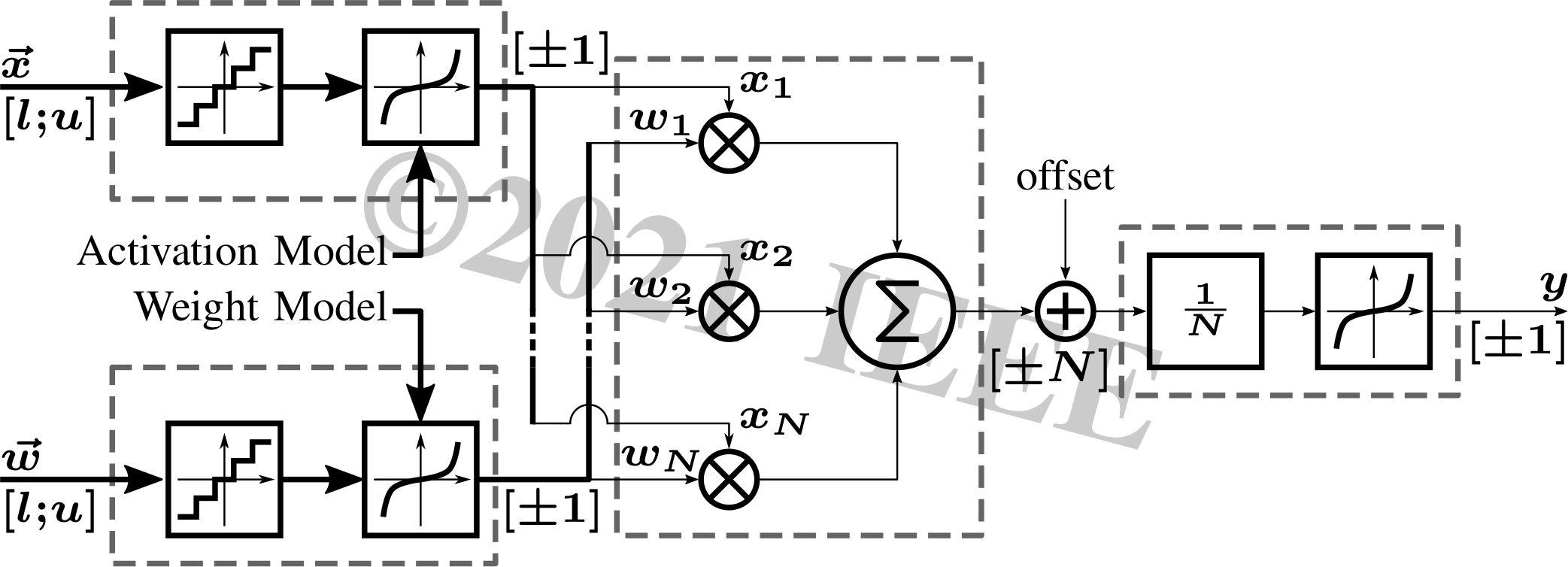

Ein Beispiel für ein solches Problem sind analoge Nichtidealitäten innerhalb der Mixed-Signal-Rechenschaltungen. Sie können durch eine Verbesserung der Schaltung reduziert werden, was jedoch mit Nachteilen bei Leistung, Fläche und/oder Geschwindigkeit der Hardware verbunden ist. Andererseits können Nichtidealitäten beim Training eines neuronalen Netzes modelliert werden um deren Auswirkungen auf das Inferenz-Ergebnis zu minimieren.

In diesem Projekt werden beide Ansätze parallel zueinander untersucht und aufeinander abgestimmt. Die Optimierung der neuronalen Netze orientiert sich dabei an simulierten und gemessenen Hardware Spezifikationen, während die optimierten neuronalen Netze die Effizienz der implementierten Hardware signifikant erhöhen.

Zukünftige Arbeiten werden weitere Hardware implementieren um umfangreiche Messergebnisse zu erhalten, womit noch detailiertere Regeln für das Co-Design von Hardware und Algorithmus abgeleitet werden können. Dies soll neue Möglichkeiten für den Einsatz von KI-Algorithmen nahe dem Endgerät (EdgeAI) eröffnen.

Publikationen

- Conrad, J.; Wilhelmstätter, S.; Mandry, H.; Kässer, P.; Abdelaal, A.; Asthana, R.; Belagiannis, V.; Ortmanns, M.

PSumSim: A Simulator for Partial-Sum Quantization in Analog Matrix-Vector Multipliers

IEEE International Symposium on Circuits and Systems (ISCAS), London, United Kingdom

Mai 2025

DOI: 10.1109/ISCAS56072.2025.11043442

- Conrad, J.; Wilhelmstätter, S.; Asthana, R.; Belagiannis, V.; Ortmanns, M.

Differentiable Cost Model for Neural-Network Accelerator Regarding Memory Hierarchy

IEEE Transactions on Circuits and Systems I: Regular Papers ( Early Access )

Oktober 2024

DOI: 10.1109/TCSI.2024.3476534

- Conrad, J.; Kauffman, J. G.; Wilhelmstätter, S.; Asthana, R.; Belagiannis, V.; Ortmanns, M.

Confidence Estimation and Boosting for Dynamic-Comparator Transient-Noise Analysis

22nd IEEE Interregional NEWCAS Conference (NEWCAS)

September 2024

DOI: 10.1109/NewCAS58973.2024.10666354

- Conrad, J.; Jiang, B.; Kässer, P.; Belagiannis, V.; Ortmanns, M.

Nonlinearity Modeling for Mixed-Signal Inference Accelerators in Training Frameworks

28th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Dubai, UAE, 2021, pp. 1-4

DOI: 10.1109/ICECS53924.2021.9665503

- Conrad, J.; Wilhelmstätter, S.; Asthana, R.; Belagiannis, V.; Ortmanns, M.

Too-Hot-to-Handle: Insights into Temperature and Noise Hyperparameters for Differentiable Neural-Architecture-Searches

6th IEEE International Conference on Artificial Intelligence Circuits and Systems (AICAS), Abu-Dhabi, UAE, 2024, pp. 557-561

DOI: 10.1109/AICAS59952.2024.10595971

Dieses Projekt wird durch die Deutsch Forschungsgesellschaft (DFG) unter Projektnummer BE 7212/7-1 | OR 245/19-1 gefördert.

Projektpartner sind Prof. Dr. Vasileios Belagiannis und M.Sc. Rohan Asthana vom Lehrstuhl für Multimediakommunikation und Signalverarbeitung, Friedrich-Alexander-Universität Erlangen-Nürnberg.