Digital Stimulation Control and Protocol for Flexible Neural Stimulators

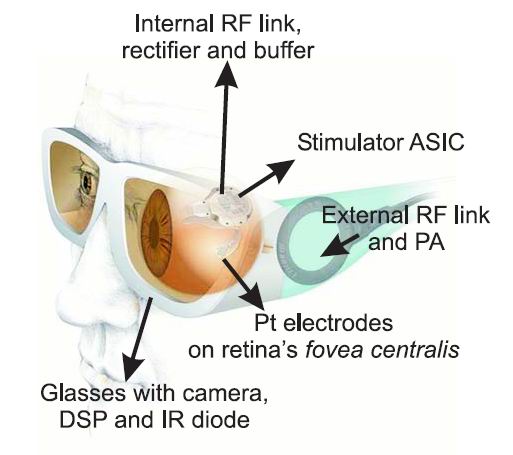

A neural prosthesis is a real-time electronic device that interfaces between the external world and the human neural system. This device has been used to restore sensory and motor functions which are lost through injuries or diseases. Usually, the central nervous system (CNS) receives information from the associated biological sensors such as eyes and ears. The dysfunction of the sensory system, however, can block the perception of the outside world. By having a neural prosthesis device, the linkage between the artificial sensors such as video camera or microphone and the CNS is established.

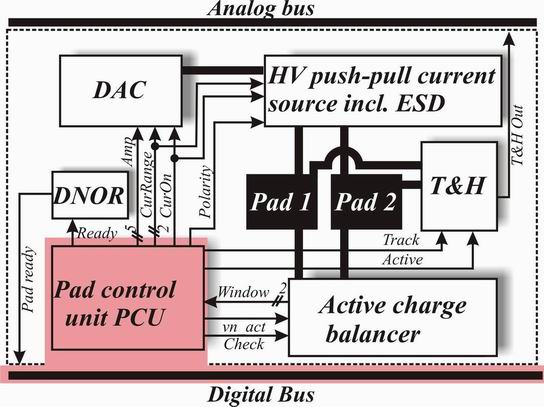

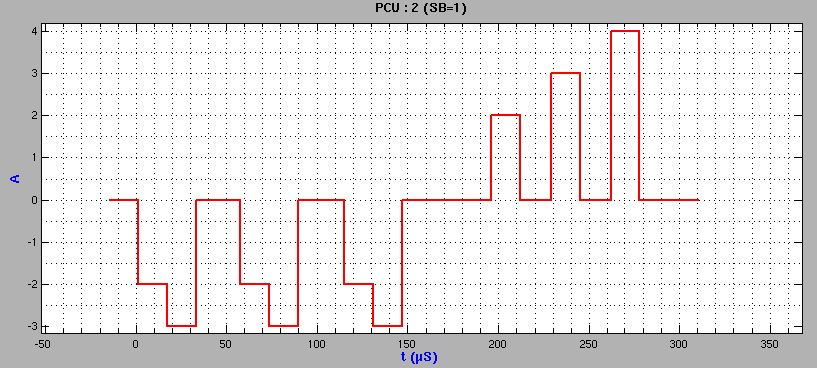

Over the last two decades and up until today various kinds of neural prosthetic chips have been developed such as retinal implant, cochlear implant and neuromuscular implant. Most of the existing electrical stimulator or neural prosthetic devices however, are designed to operate for specific function or application due to the limited variety of waveform pattern generation. This specific and limited operation has disabled the optimum usage of the neural implant chip. Motivated by the discrepancies of the existing neural implant chip, a universal neural implant chip with flexible stimulation protocol and reduced size is proposed. The execution of this flexible stimulation protocol such as the generation of arbitrary stimulation patterns, the selection and activation of several types of charge balancing circuitries, the electrode impedance measurement and the distribution of data are realized using digital chip design.

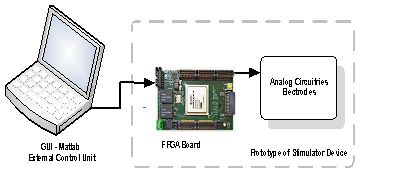

A prototype of stimulator device is currently being developed for a system level testing purposes. The digital stimulator design is downloaded into an FPGA board which is connected to a computer and analog circuitries. A GUI using MATLAB is developed to mimic the functionality of an external control unit such as controlling and monitoring the neural implant chip operation.

A standard AMS 0.35µ CMOS technology is used for ASIC implementation. The digital stimulator architecture is simulated using Cadence NCLaunch and synthesized using Synopsys Design Compiler software. The synthesization and optimization of the digital design architecture is done by taking the timing, the area and the power constraints into consideration. Power reduction technique and power analysis will also be performed by using the Synopsys Power Compiler.

Projektleiter

Ehem. Projektmitglieder

Dr.-Ing. E. Noorsal