Physical Unclonable Functions (PUFs)

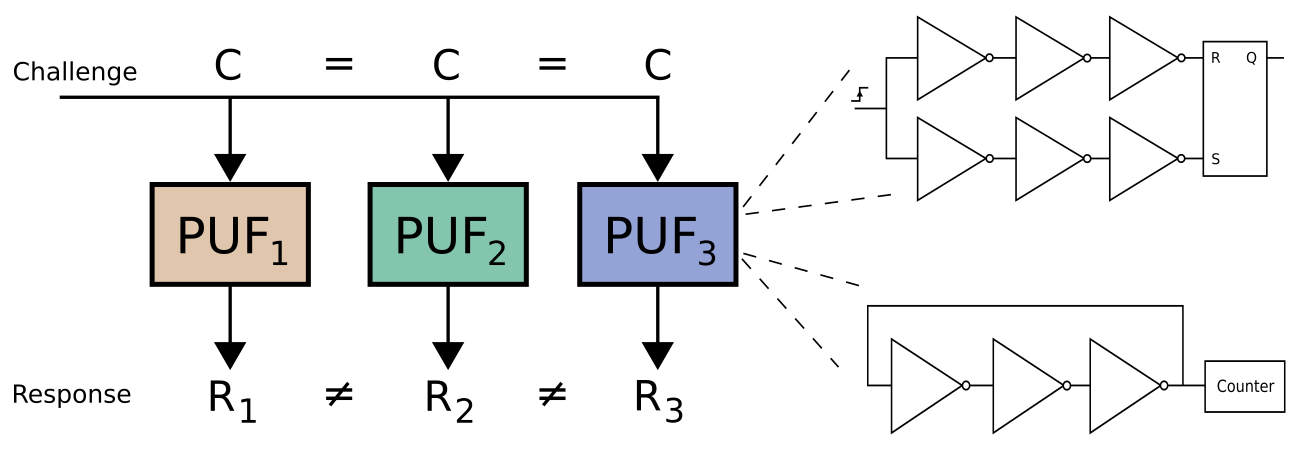

Im Lauf des letzten Jahrzehnts haben Physikalisch Unklonbare Funktionen (PUFs) sich als fester Bestandteil auf dem Gebiet der Kryptographie und der Authentifizierung etabliert. Diese basieren auf physikalischen Abweichungen, die sich aufgrund beschränkter Präzision während des Herstellungsprozess ergeben. PUFs bieten daher hervorragende Eigenschaften für die genannten Forschungsfelder, inbesondere Einzigartigkeit, Unvorhersagbarkeit und Unklonbarkeit. Bei Anregung mit einem digitalen Eingangssignal erzeugen PUFs eine digitale Ausgabe, welche vollständig auf den jeweils einzigartigen Abweichungen einer PUF basiert.

Abgesehen von einigen wenigen neuartigen PUF-Architekturen und verschiedenen Manifestationen von Abweichungen konzentrieren sich aktuelle Publikationen hauptsächlich auf die Verbesserung existierender PUFs im auf Systemebene und durch verbesserte Kodierungs- und Fehlerkorrekturtechniken. Zudem wird der Großteil neuartiger oder verbesserter Ausführungen nur simuliert oder auf FPGAs implementiert.

Der Fokus dieses Projekts ist die darüber hinausgehende Aufwertung analoger und mixed-signal PUF-Architekturen. Hierbei sollen analoge Designtechniken angewendet werden, um existierende PUF-Primitive und -schaltungen auf Transistorebene zu verbessern. Ein Ziel ist es, einen signifikanten Fortschritt in Bezug auf die Stabilität und Qualität von PUF-Ausgaben zu erreichen. Insbesondere soll die Unempfindlichkeit gegenüber Umgebungs- und Rauscheinflüssen erzielt werden sowie eine deutliche Unterscheidbarkeit und ein stabiles Ausleseverhalten gewährleistet werden. Andere Nebenthematiken, die sich aus dieser Zielsetzung ergeben, sind verbesserte Simulationsmethoden solcher verbesserter PUF-Architekturen und die Entwicklung neuartiger PUF-Architekturen selbst.

Ein zweites Hauptthema dieses Projekts ist die Untersuchung von beliebiger Industrie- und Anwendungselektronik und jeglicher Art von mixed-signal ICs auf intrinsische PUF-Funktionalität. Die Verwertung bereits existierender Schaltungen mit inhärenten und eindeutigen Abweichungen, sofern vom umgebenden System selbst zugreifbar und messbar, bietet eine schnelle und billige Möglichkeit PUF-Architekturen zu implementieren. Dieser Ansatz wurde bereits exzessiv auf verschiedene Arten von Speichern untersucht und soll im Rahmen des Projekts auf weitere Bereiche erweitert werden.